电磁兼容技术的多层PCB布线设计需要注意什么

电子计算机科学与技术是一门新兴的、综合性的学科,主要研究电子计算机中的电磁干扰和抗干扰问题。EMI是指电子设备或系统在规定的电磁环境水平下,不会因电磁干扰而降低其性能指标,同时其自身产生的电磁辐射不会超过限值水平,不会影响其他系统的正常运行,达到设备和设备、系统和系统之间互不干扰,共同可靠工作的目的。

EMI(EMI)是由电磁干扰源通过耦合路径向敏感系统传输能量而产生的,它包括三种基本形式:导线传导、公用地线传导、空间辐射或近场耦合。实际应用表明,即使电路原理图设计正确,但印刷线路板设计不当,也会对电子设备的可靠性产生不利影响,因此,确保印刷线路板的电磁兼容性是整个系统设计的关键,本文主要论述了电磁兼容技术及其在多层印刷线路板设计中的应用。

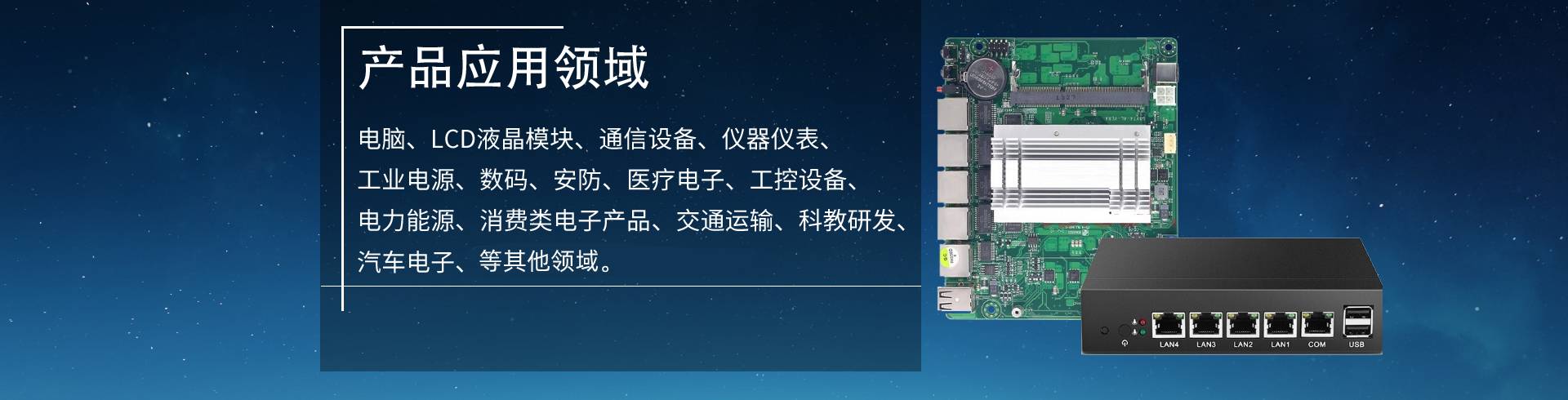

印刷电路板是电子产品中电路元件和装置的支撑部件,它提供了电路元件和装置之间的电气连接,是各种电子装置的最基本部件。目前,大型、超大规模集成电路已经广泛地应用于电子设备中,并且元件在印制板上的安装密度越来越大,信号的传输速度越来越快,由此引起的EMC问题也日益突出。印刷电路板分为单面板(单层板)、双板(双层板)和多层板。单板和双板通常用于低、中密度布线及低集成度电路,而多层板采用高密度布线及高集成度电路。单、双板不适合高速电路,单、双面布线无法满足高性能电路的要求,而多层布线技术的发展为解决上述问题提供了可能,而且其应用也日益广泛。

多层配线的特点。

电路板是由有机和无机介质材料组成,具有多层结构,各层之间通过过孔连接,过孔镀层或填充金属材料即可实现各层之间的电信号导通。由于以下几个特点,多层布线得到了广泛的应用:

多层板材内设有专用电源层,地线层。电源层可作为噪声源,减少干扰;同时电源层可为系统所有信号提供回路,消除公用阻抗耦合干扰。降低供电系统中供电线路的阻抗,从而降低公用阻抗干扰。

(2)多层板采用专门的地线层,所有信号线都有专门的地线。信号线的特点:阻抗稳定,匹配性好,减少反射引起的波形失真;采用特殊的地线层,增大信号线与地线之间的分布电容,减小串扰。

第三,印刷电路板的叠片设计。

PCB板的接线规则。

多层板的电磁兼容分析可依据克希霍夫定律和法拉第定律进行。按照克希霍夫定律,任何从信号源到负载的时域传输信号都必须具有最低的阻抗路径。

带多层板的PCB通常用于高速高性能系统,其中的多层板可用于直流(DC)电源或地参考面。由于有足够的层数作为电源或地层,这些平面通常不会被分割成实体平面,所以不必在同一层中放置不同的DC电压。这一层将作为电流回路,回流到与之相邻的传输线上的信号。构建低阻抗电流回路是这类平面层EMC的首要目标。

信号层分布于参考面实体层之间,它们可以是对称带状线或不对称带状线。多层板的结构和布局以12层板为例进行说明。它的层次结构是T-P-S-P-S-P-B,其中T是最上层,P是参考平面,S是信号层,B是最下层。由上到下依次为1层、2层、…、12层。作为元件的上、下焊盘,信号在上、下之间不能有长距离传输,这样可以减少走线的直接辐射。非兼容信号线应该彼此隔离,其目的是避免彼此间的耦合干扰。高频率和低频率,大电流和小电流,数字和模拟信号线是不相容的,元件布置应将不相容元件放置在印制板的不同位置,信号线布置时仍应注意将其隔离。在设计中应注意三个问题:

决定哪一个参考层会包含用于不同DC电压的多个电源区。假定第十一层具有多个DC电压,则设计人员必须使高速信号尽可能远离第十层和底层,因为回路电流不能穿过第十层以上的参考平面,需要采用缝线电容;第三、五、七和九层是高速信号的信号层。关键信号的走线尽可能是单向布置的,这样就可以在优化层上确定可能的走线通道数。各层之间的信号走线应该彼此垂直,这样可以减少线间电场和磁场的耦合干扰,第三、七层可以设“东西”走线,第五、九层设“南北”走线。在哪一层的布料要根据它到达目的地的方向。

(2)高速信号走线时的层数变化,以及在一条独立走线中使用哪一层,保证返回电流从一个参考面流向所需的新参考面。这是为了减小信号环面积,减少回路差模电流辐射和共模电流辐射。回路的辐射强度与回路的面积成正比。事实上,最好的设计并不需要改变参考面,只需要改变参考面的一面,而只需要将其换回另一面。例如信号层的组合可作为信号层对使用:第3、5、7、7、9,这样就可以在东西和南北两个方向上形成布线组合。但第三和第九层的组合则不能使用,因为这需要返回电流从第四层流向第8层。虽然去耦电容可以放置在过孔附近,但是在高频下,由于引线和过孔电感的存在,它会失去作用。而这样的走线将使信号环面积增加,不利地减小了电流辐射。

(3)选择基准层的直流电压。在这种情况下,由于处理器内部信号处理速度较快,导致电源/地参考管脚产生了大量噪声。所以,在为处理器提供相同的DC电压以及尽可能高效地使用去耦电容器时,使用去耦电容器是很重要的。减小这些元件电感的最佳方法是将走线连接得尽可能短,尽可能宽,过孔尽量短,过粗。

当第二层被分配为“地”,而第四层被分配为处理器的电源时,过孔距离越远,处理器的顶层和去耦电容器应该越短。在延伸至板底的过空处没有任何重要电流,短路时也没有天线作用。层叠设计布局的参考配置列于表1。

20-H规则,3-W规则。

确定多层PCB板电容设计中多层板电容电源层与板边之间的距离,以及解决印刷条之间的距离,有两个基本原则:20-H法和3-W法。

20-H原理:RF电流通常存在于电源平面的边缘,这是因为磁通之间的连接,当采用高速数字逻辑和时钟信号时,RF电流相互耦合,如图1所示。为了减少这种影响,电源平面的物理尺寸应至少比最靠近地平面的物理尺寸(H为电源平面与地平面之间的距离)小20H,电源平面的边缘效应一般发生在10H左右,20H时,大约10%的磁通被阻断,如果要达到98%的磁通,需要100%的边界值,如图1所示。由20-H规则确定电源平面与包括覆铜板厚度、预填料和绝缘隔离层在内的最近接地平面之间的物理距离。采用20-H可使PCB的共振频率增加。

3-W规则:当两个印刷线之间的间距较小时,会产生电磁串扰,从而影响相关电路的正常工作,为了避免这种干扰,印刷线的间距应不小于3倍,即不小于3W(W是印刷线的宽度)。印刷线宽与线阻抗要求有关,过宽影响布线密度,过窄影响信号完整性,过窄影响传输终端的强度。3-W原理的基本应用对象为时钟电路、差分对和I/O端口布线。“3-W原理”只是简单地指出了串扰能量衰减70%的电磁通量边界,如果要求更高,如保证串扰能量衰减98%的电磁通量边界必须采用10。